導航衛星 現代文明的時空坐標

在浩瀚的宇宙中,一群靜默的“天眼”正以極高的精度環繞地球運行,它們就是導航衛星。這些由人類智慧創造的航天器,構成了覆蓋全球的衛星導航系統,不僅深刻改變了我們的生活方式,也成為了支撐現代社會運轉不可或缺的基礎設施。

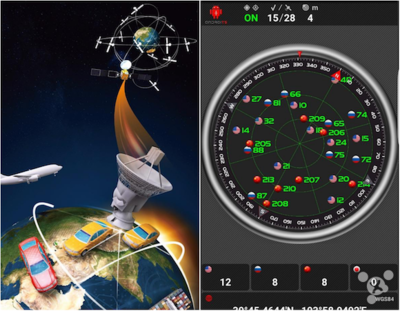

導航衛星系統的工作原理基于精確的時間測量與幾何計算。每顆衛星持續播發包含自身位置與時間戳的信號,地面接收設備通過接收多顆衛星的信號,計算出信號傳播的時間差,進而確定自身在地球上的三維坐標、速度與時間。這一過程,實現了從“仰望星空”到“定位自我”的跨越。

目前,全球有四大成熟的衛星導航系統:美國的GPS(全球定位系統)、俄羅斯的GLONASS(格洛納斯系統)、歐盟的Galileo(伽利略系統)和中國的北斗衛星導航系統。它們共同構成了一個多層次、互補的全球導航衛星系統(GNSS)網絡。其中,中國的北斗系統作為后起之秀,實現了從區域服務到全球覆蓋的跨越,其獨特的短報文通信等特色服務,展現了技術發展的多樣性與自主創新的重要性。

衛星導航的應用已滲透到社會經濟的各個毛細血管。在日常生活中,它為我們提供精準的出行導航,支撐著外賣、快遞、共享出行的即時服務;在交通運輸領域,它是航空航海、智能交通、物流調度的“智慧中樞”;在專業領域,它服務于精準農業、地質勘探、防災減災、科學考察,極大地提升了生產效率與安全系數;在國家安全層面,它更是現代軍事行動的“眼睛”,為指揮控制、武器制導提供關鍵支持。可以說,沒有衛星導航,當今世界的許多高效協同與精準操作都將難以實現。

衛星導航系統的發展也面臨著挑戰與未來展望。其信號容易受到遮擋、干擾甚至欺騙,在城市峽谷、室內或復雜電磁環境下,精度和可用性會下降。因此,增強系統魯棒性、提升抗干擾能力是技術發展的重點。導航衛星正朝著更高精度、更強融合、更廣服務的方向演進。通過與其他技術(如慣性導航、5G通信、物聯網、人工智能)的深度融合,構建天地一體、無縫覆蓋的定位、導航與授時(PNT)體系,將成為大勢所趨。下一代導航衛星將具備更高的自主運行能力、更強大的互操作性與更豐富的服務功能,為自動駕駛、智慧城市、元宇宙等新興領域奠定堅實基石。

從仰望星空到掌控時空,導航衛星與衛星導航技術是人類將科學夢想轉化為現實力量的典范。它不僅是測量位置的工具,更是連接物理世界與數字世界、賦能全球數字化發展的關鍵橋梁。隨著技術的不斷突破與應用場景的持續拓展,這群寂靜的太空信使,將繼續為我們指引前行的方向,繪制更加精準、智能的未來世界圖景。

如若轉載,請注明出處:http://www.jenjenhouse.cn/product/59.html

更新時間:2026-04-14 09:36:09